WHAT DO WE STUDY?

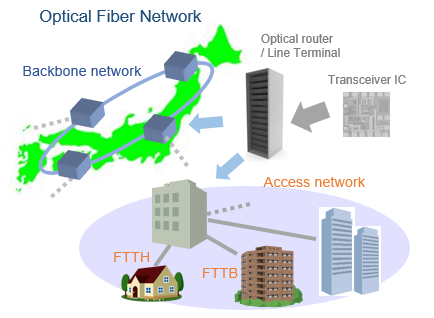

現在の研究テーマは、これからの高度情報社会を支える情報通信システム用集積回路に関する物です。爆発的に増え続けるインターネット・トラフィックに対応するために、情報通信用ネットワークの大容量化・高効率化が望まれています。特に、光ネットワークシステムは、光の高速性や、電磁波としての波の特性を利用した大容量通信が可能で、基幹ネットワークからアクセスネットワークまで導入が進んでいます。本研究室では光通信技術と信号処理に優れる電気回路との融合により高度化を目指しています。

主な研究テーマ:

- 光パケット伝送用光送受信回路の高度化、高効率化、低電力化

- 高度な光ネットワークが可能な適応型光インターフェース

- ディジタル制御によるアナログ回路の高機能化